# Quality and Reliability

## Report

# FY 2017

## Table of Contents

| CHAPTER 1, ZILOG'S QUALITY CULTURE                           | 5    |

|--------------------------------------------------------------|------|

| RELIABILITY AND QUALITY ASSURANCE POLICY STATEMENT           | 6    |

| ZILOG OUALITY POLICY                                         | 6    |

| ZILOG'S QUALITY AND RELIABILITY PROGRAM                      | 7    |

| Training                                                     |      |

| Order Acknowledgment Policy                                  | 7    |

| Test Guardbanding                                            | 7    |

| Product Characterization                                     |      |

| Process Qualification                                        | 8    |

| Product $\widetilde{Q}$ ualification                         |      |

| PPM Measurement, Direct and Indirect                         |      |

| FIT Measurement Direct and Indirect                          |      |

| Field Quality Engineers                                      |      |

| Product Analysis                                             | 9    |

| Total Quality Program                                        |      |

| Environmental Protection Recycling                           |      |

| ZILOG ENVIRONMENTAL, HEALTH AND SAFETY POLICY                | . 10 |

| ISO CERTIFICATION                                            |      |

| ISO CERTIFICATION OF FOUNDRIES/SUBCONTRACTORS                | . 11 |

| QUALITY AND RELIABILITY TREND CHARTS                         | . 12 |

| FIT Rate (FIT = Failure in Time: Failures per Billion Hours) |      |

| PPM Electrical                                               | . 12 |

| CHAPTER 2, CUSTOMER QUALITY SUPPORT SYSTEM                   | . 13 |

| CUSTOMER FAILURE ANALYSIS/CORRELATION PROCEDURE              |      |

| Guideline Information Needed By The Factory With CFA's       | . 15 |

| Summary of QC Test Equipment                                 |      |

| CUSTOMER NOTIFICATION SYSTEM                                 | . 19 |

| CHAPTER 3, QUALIFICATION REQUIREMENTS                        |      |

| Product/Process Qualification Requirements                   | . 21 |

| Product/Process Qualification Requirements                   | . 21 |

| Package Qualification Requirements                           | . 23 |

| Zilog Package Qualification Summary                          | . 24 |

| CHAPTER 4, QUALITY MONITOR SYSTEMS                           | . 25 |

| FAILURE RATE PREDICTION CALCULATIONS                         | . 26 |

| ESD TESTING METHODOLOGY                                      | . 28 |

|                                                              |      |

| LATCHUP TESTING METHODOLOGY                                                                              |    |

|----------------------------------------------------------------------------------------------------------|----|

| ZILOG'S RELIABILITY SUMMARY                                                                              |    |

| EARLY LIFE                                                                                               |    |

| LONG TERM LIFE                                                                                           |    |

| PRESSURE POT                                                                                             |    |

| TEMPERATURE CYCLE                                                                                        |    |

| HIGHLY ACCELERATED STRESS TEST                                                                           |    |

| PACKAGE INTEGRITY TEST                                                                                   |    |

| BurnIn Life Test                                                                                         |    |

| Pressure Pot Test, 121°C, 2 ATM                                                                          |    |

| Temperature/Humidity Test                                                                                | 34 |

| Temperature Cycling Test, Condition C, -65°C To 150°C                                                    | 35 |

| Highly Accelerated Stress Test (HAST), 140°C , 85% RH, At 2 ATM                                          | 36 |

| Package Integrity Test Error! Bookmark not def                                                           |    |

| C-Mode Scanning Acoustic Microscope Monitor                                                              | 37 |

| CHAPTER 5, PACKAGE & TEST INFORMATION                                                                    |    |

| Package types                                                                                            | 39 |

| Technology Data                                                                                          | 39 |

| Pre/Post Packaging Device Test Procedures                                                                | 40 |

| Reduction of Hazardous Substances (RoHS                                                                  | 41 |

| Plastics Process Flow                                                                                    | 43 |

| Plastic-Standard Assembly/Test Process                                                                   | 44 |

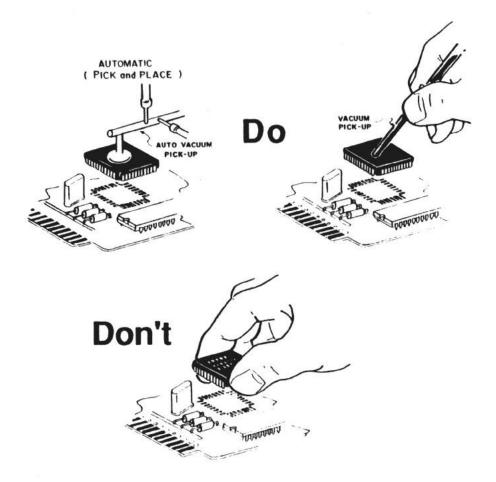

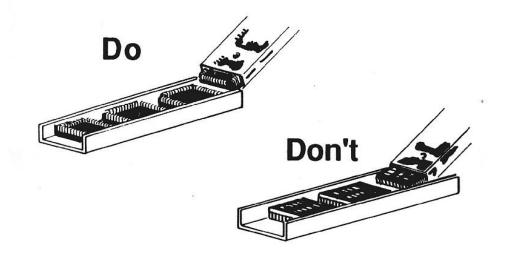

| The Handling and Storage of Surface Mount Devices                                                        | 45 |

| Handling                                                                                                 |    |

| Lead Protection                                                                                          | 46 |

| ESD Protection                                                                                           | 46 |

| Storage Unpacking Caution                                                                                | 47 |

| Soldering                                                                                                | 47 |

| Desoldering                                                                                              |    |

| THERMAL CHARACTERISTICS                                                                                  | 48 |

| Calculation of Device Junction Temperature                                                               | 48 |

| Device $\theta_{JA}$ , $\theta_{JC}$ Table Summary Of Thermal Characteristics For Zilog Plastic Packages |    |

| CHAPTER 6, QUALITY SYSTEMS                                                                               |    |

| QUALITY SYSTEMS                                                                                          |    |

| SUBCONTRACTING                                                                                           |    |

| LOT TRACEABILITY                                                                                         |    |

| AVAILABILITY OF DOCUMENTATION ON MONITORING                                                              | 51 |

| QUALITY DATA                                                                                             |    |

| TESTING (QA/Operating)                                                                                   |    |

| TEST TAPE SUPPORT                                                                                        |    |

| WHAT HAPPENS WHEN FAILURES OCCUR?                                                                        |    |

| WHEN MANUFACTURING IS PERFORMED OFFSHORE, WHAT ARE THE CONTROLS                                          |    |

| AVAILABILITY OF PROGRAMMING FACILITIES                                                                   |    |

| QA AUDIT                                                                                                 |    |

| *                                                                                                        |    |

| DOCUMENT CONTROL SYSTEM                     |  |

|---------------------------------------------|--|

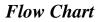

| Flow Chart                                  |  |

| CHAPTER 7, QUALITY AND RELIABILITY GLOSSARY |  |

Chapter 1, Zilog's Quality Culture

## **CHAPTER 1**

# Zilog's Quality Culture

# Zilog<sup>®</sup> An IXYS Company

### Zilog's Quality Culture

#### **RELIABILITY AND QUALITY ASSURANCE POLICY STATEMENT**

Zilog's philosophy towards quality has been consistently aimed at continuous product improvement and optimization of processes associated with the design, manufacture, test and delivery of products that conform to all established requirements for total customer satisfaction.

It has been a Zilog tradition that the customer is the main driving force in a company-wide goal to achieve the highest quality possible. Through excellent management of its personnel, equipment, materials, environmental resources, and subcontractors Zilog is well positioned for success.

#### ZILOG QUALITY POLICY

#### QUALITY POLICY

#### Delight our Customers by...

- Doing the job right the first time

- · Making and meeting commitments

- Excelling through planning and teamwork

- Driving continual improvement with Best Known Methods

- Respecting team members and making Zilog a great place to work

sdaley@zilog.com

Director of Quality and Reliability

Zilog - an IXYS Company

#### ZILOG'S QUALITY AND RELIABILITY PROGRAM

Zilog's Quality and Reliability Program is based on careful study of the principles laid down by such pioneers as W. E. Deming and J. M. Juran. Even more importantly, we have benefited from the observation and practical implementation of those principles as practiced in Japanese, European and American manufacturing facilities.

The Zilog program begins with employee involvement. Whether the judgment of our performance is based on perfection with incoming inspection, trouble free service in the field, or timely and accurate customer service, we recognize that our employees ultimately control these factors. Hence, our quality program is broadly shared throughout the organization.

#### Training

The integrity of our product design depends on the skills of our employees. Zilog training emphasizes the fundamentals involved in product design and processing for quality and reliability.

Customer Service, an important aspect of Zilog's quality performance as a vendor, also depends upon our people clearly understanding their jobs and our obligations to our customers. This aspect of training is also a part of the overall curriculum administered by Zilog.

#### **Order Acknowledgment Policy**

One definition of vendor quality performance is that the vendor "does what he or she promises or acknowledges." Acceptable reliability and quality is achieved only if Zilog and the customer are in agreement on product and delivery specifications.

#### Test Guardbanding

No physical attribute is absolute. Customers' test methods may differ from Zilog's due to variations in test equipment, temperature or specification interpretation. To ensure that every Zilog product performs to full customer expectations, Zilog uses a "waterfall" methodology in its testing. The first electrical tests made on the circuit for both AC and DC parameters, at the wafer probe operation, are guardbanded to the final test specifications. The final test specifications for both AC and DC parameters, in turn, are guardbanded to the quality control outgoing sample. The quality control outgoing sample is guardbanded to data sheet specifications. This technique of "waterfall" guardbanding eliminates circuits that may be marginal to the customer's expectations long before they get to the shipping container.

#### **Product Characterization**

Every Zilog product design is evaluated over extremes of operating temperature, supply voltage, and clock frequency prior to production release. This information permits the proper guardbanding of the test program waterfall and identification of any marginal "corners" in design tolerances.

A product characterization summary, which details the more important tolerances identified in the process of this exhaustive product design evaluation, is available to Zilog's customers.

#### **Process Qualification**

Zilog also qualifies every process prior to production by an exhaustive stress sequence performed on test chips and on representative products. Once a process regime is qualified, a process re-qualification is performed any time there is a major process change.

#### **Product Qualification**

In addition to characterization, every new Zilog product design is fully qualified by a comprehensive series of life, electrical, and environmental tests before release to production. Whenever possible, both industry standard environmental and life tests are employed. Again, a qualification summary is available to our customers that details certain key life and environmental data taken in the course of these evaluations. Please see Qualification Requirements for an example of the Zilog Package Qualification Summary and Device Qualification Summary.

#### PPM Measurement, Direct and Indirect

It is frequently said that if you want to improve something, you need to measure it. Therefore, Zilog measures its outgoing quality "parts per million" by the maintenance of careful records on the statistical sampling of production lots prepared for shipment. This information is then translated to a statement of our parts per million outgoing quality performance.

Of course, it is one thing for Zilog to think it is doing a good job in outgoing product quality and it is another for a customer to agree. Therefore, we ask certain key customers to provide us with their incoming inspection data that helps us calibrate our outgoing performance in terms of the actual results in the field. The fact that Zilog has been awarded "ship to stock" status by many customers testifies to our success in this area.

#### FIT Measurement Direct and Indirect

Just as Zilog records its outgoing quality in terms of parts per million, it also measures its outgoing product reliability in terms of "FITS" or Failures per billion device hours. This calculation is done by using the results of weekly operating life test measurements on the circuits performed in accordance with standard specifications.

#### **Field Quality Engineers**

Zilog maintains a force of skilled Field Application Engineers, who are also trained as Field Quality Engineers. These engineers are available on immediate call to consult our customers on any problems they may be experiencing with Zilog product performance.

#### **Product Analysis**

Product Analysis facilities, staffed by experienced professionals, exist at each Zilog site to provide rapid evaluation of in-process and in-field rejects. Zilog is pleased to share product analysis reports on specific products with the customer upon request.

#### **Total Quality Program**

Zilog employees actively participate in meetings where methods are proposed, reviewed, and adopted. These meetings enable a department to do its job in a more precise and accurate manner.

#### **Environmental Protection Recycling**

Zilog is committed to an environmental protection-recycling project that is becoming an international requirement. Zilog prefers that materials used to package its finished products be recyclable and/or manufactured from recycled material. The "Recyclable" symbol can already be found on shipping boxes, tubes and reels, and on shipping trays.

#### ZILOG ENVIRONMENTAL, HEALTH AND SAFETY POLICY

#### Zilog Environmental, Health and Safety Policy

Zilog's mission is to create superior value for our stakeholders. The health and safety of our employees, and the proper care of our environment based on the defined scope of the environmental management system are of paramount importance. Zilog's concern for them is not only good corporate citizenship, it's also good business. Zilog is committed to a continually improving Environmental, Health and Safety Management System. Strict compliance with applicable EHS regulations is considered a minimal standard – neither production goals nor financial objectives shall excuse noncompliance.

The core values of Zilog's EHS Management System are to:

- Create, maintain and promote a safe and healthful workplace for all employees.

- Comply with the intent as well as the letter of all applicable EHS regulations at the Federal, State, local levels, and other requirements to which Zilog subscribes.

- Set EHS goals and objectives and measure progress toward them.

- Promote a respect for the environment among employees.

- Conserve resources and minimize waste by reducing, reusing, and recycling.

- Integrate EHS considerations into business planning, decision making, and daily activities.

- Provide the resources and training to carry out this policy.

- Prevent accidents and minimize environmental impact.

- Communicate our EHS performance.

- Respond to the concerns of the communities in which we do business.

- Support EHS public policy development.

- Encourage our contractors and suppliers to adopt EHS standards similar to our own.

- Exchange EHS knowledge and technology.

These core values build on our tradition of quality, innovation, and continual improvement.

Alan Shaw Vice President of Operations Zilog, Inc.

#### **ISO CERTIFICATION**

Zilog is extremely proud to have received the following ISO 9001:2008 certification award, which reflect the stringent quality standards to which all Zilog products are manufactured.

# FACILITY/LOCATIONCERTIFICATION RECEIVEDZilog ElectronicsISO9001:2008Philippines, Inc. (ZEPI)BSI Management SystemsManila, Philippines- Subcontractor Management,Assembly and Test of Power Devices,DCB Laser Scribe, Warehousing andShipment- Subcontractor Management,

#### (\*ISO - International Standards Organization)

#### ISO CERTIFICATION OF FOUNDRIES/SUBCONTRACTORS

| FACILITY                 | LOCATION         | PROGRAM          |

|--------------------------|------------------|------------------|

| Wafer Foundries:         |                  |                  |

| UMC                      | Taiwan           | ISO 9001/TS16949 |

| TSMC                     | Taiwan           | ISO 9001/TS16949 |

| XFAB                     | USA              | ISO 9001/TS16949 |

| Assembly Subcontractors: |                  |                  |

| UNISEM                   | Batam, Indonesia | ISO 9001/TS16949 |

| Amkor                    | Manila, Korea    | ISO 9001/TS16949 |

| ASEK                     | Taiwan           | ISO 9001/TS16949 |

| UTL                      | Thailand         | ISO 9001/TS16949 |

| Greatek                  | Taiwan           | ISO 9001/TS16949 |

| LIKOM                    | Malaysia         | ISO 9001         |

|                          |                  |                  |

| Test Subcontractors:     |                  |                  |

| Ardentec                 | Taiwan           | ISO 9001/TS16949 |

| ASET                     | Taiwan           | ISO 9001/TS16949 |

| Amkor                    | Manila, PI       | ISO 9001/TS16949 |

| UNISEM                   | Batam, Indonesia | ISO 9001/TS16949 |

|                          |                  |                  |

#### QUALITY AND RELIABILITY TREND CHARTS

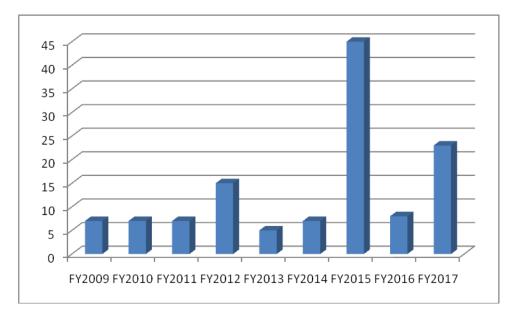

**Figure 1-1** – FIT Rate (FIT = Failure in Time: Failures per Billion Hours)

\* No failure out of sample size

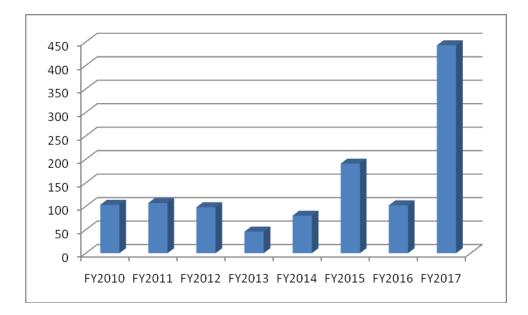

Figure 1-2 - PPM Electrical

## CHAPTER 2

# Customer Quality Support System

DC04-0001 Revision 23 Page 13 of 65

## Customer Quality Support System

#### CUSTOMER FAILURE ANALYSIS/CORRELATION PROCEDURE

Zilog has a complete Customer Failure Analysis (CFA) system. Using this system, a customer may return units for failure analysis or test correlation. The sequence of events for the CFA procedure is as follows:

- 1. Customer suspects a failure.

- 2. The customer completes a CFA request. See Figure 2-1.

- 3. A CFA request is assigned a number for tracking.

- 4. The customer returns the unit(s) to the factory.

- 5. Product/Test Engineering performs a go/no-go electrical test.

- 6. The unit(s) and test results are given to the Failure Analysis Engineer.

- 7. If the unit(s) fail the test, the Failure Analysis Engineer performs electrical and physical analysis, and generates a CFA report.

- 8. If the unit(s) pass the test, the Failure Analysis Engineer generates a CFA report and returns the unit(s) to the customer.

- 9. Our goal is to provide a complete CFA report within 10 working days from the time the unit(s) are received.

Zilog and the customer will work together to reduce all types of failures to zero. The CFA procedure is one of several communication tools that can be used to achieve this goal, proving its overall effectiveness since its inception in 1985.

#### Figure 2-1

CFA Request-Failure Analysis Questionnaire Form

Purpose: To eliminate time spent researching a failed component/part history in order to concentrate on finding the root cause of failure or complaint by the customer

| FAILURE ANALYSIS QUESTIONNAIRE |                   |                          |                     |                         |             |

|--------------------------------|-------------------|--------------------------|---------------------|-------------------------|-------------|

| ZiLOG Confidential             |                   | SOP0929-I<br>Page 1 c    |                     |                         | Revision 07 |

| GENERAL INFORMATI              | ION:              |                          |                     |                         |             |

| Initiated By:                  |                   | Date:                    |                     | B.U.:                   |             |

| Customer Name:                 |                   |                          |                     |                         |             |

| Customer Address:              |                   |                          |                     |                         |             |

| Phone No:                      |                   |                          | Under Warranty?     | Yes No                  |             |

| NOTE: Failure analysis of      | f out of warran   | ty parts is for inforn   | uation only.        |                         |             |

| PART INDENTITY:                |                   |                          |                     |                         |             |

| Device:                        | Date/bb Code:     |                          |                     | Total # devices in lot: |             |

| Qty. devices tested/inspecte   | ed: Qty. b        | eing returned:           |                     | Qty. of failed devices: |             |

| Customer Application:          |                   |                          |                     |                         |             |

|                                |                   |                          |                     |                         |             |

| FAILURE DESCRIPTIO             | N:                |                          |                     |                         |             |

| Incoming:                      | Assembly:         | Final Te                 | est:                | Field Return:           |             |

| Low Noise Option? 🗌 Ye         | s 🗌 No            | How long in servic       | e before failure oc | curred?                 |             |

| Was part removed with any      | v other parts?    | 🗌 Yes 🗌 No               |                     |                         |             |

| Did failure follow part?       |                   | Yes No                   |                     |                         |             |

| Additional processing temp     | eratures which    | <br>part had seen before | failure occurred:   |                         |             |

| Is this a new application for  | r this device?    | 🗌 Yes 🗌 No               |                     |                         |             |

| Is this a new failure mode?    |                   | Yes No                   |                     |                         |             |

| Is there a Customer board o    | or test program a | wailable for use at Z    | iLOG?               | Yes 🗌 No                |             |

| Are there failing and passin   | ng samples avail  | able for correlation v   | work?               | Yes No                  |             |

| Process steps part had seen    | up to time of fa  | ilure:                   |                     |                         |             |

| OTP RETURNS:                   |                   |                          |                     |                         |             |

| Programmer used:               |                   | Software R               | ev:                 | Checksum:               |             |

| Option Bits Selected:          |                   |                          |                     |                         |             |

| NOTE: For the most thoron      | ugh analysis, ple | ease include a Hex fi    | le of the Customer  | 's code.                |             |

| ADDITIONAL DETAILS             | š:                |                          |                     |                         |             |

|                                |                   |                          |                     |                         |             |

|                                |                   |                          |                     |                         |             |

|                                |                   |                          |                     |                         |             |

|                                |                   |                          |                     |                         |             |

|                                |                   |                          |                     |                         |             |

|                                |                   |                          |                     |                         |             |

|                                |                   |                          |                     |                         |             |

|                                |                   |                          |                     |                         |             |

| Equipment At ZEPI             | Brand                  | Usage                        |

|-------------------------------|------------------------|------------------------------|

| ISOMET Low Speed Saw          | Buehler                | Cross-Section Analysis       |

| Curve Tracer                  | Tektronix 576/370B/577 | Bench Check                  |

| ESD Tester                    | IMCS 700               | VZAP Testing                 |

| Polimet Polisher              | Buehler                | Cross-Section Analysis       |

| High Power Scope              | Olympus                | External/Internal Visual     |

|                               | Orympus                | Inspection                   |

| Low Dower Score               | Olympus / ABCELLON     | External/Internal Visual     |

| Low Power Scope               | Western Dynamics       | Inspection                   |

| Decapper                      | PS102W                 | Decapping of Plastic Devices |

| Hot Plates                    | 3D Ready-Heat / Lab    | Solderability-Steam Aging    |

|                               | Companion              |                              |

| Pressure Cooker               | Electric Steroclave    | Reliability Test             |

| SEM & EDX                     | Leica S420             | Visual & Elemental Analysis  |

| Digital Multimeter            | Fluke                  | Latchup Test                 |

| Timer                         | Gralab                 | Timed Operations             |

| Profile Projector             | Mitutoyo               | Dimensional Inspection       |

| Temp Cycle (TSE 11A)          | Escpec                 | Temperature Cyling           |

| Mechanical Shock Tester       | Lansmont               | Mechanical Shock Test        |

| VVF Test                      | Unholtz-Dickie         | VVF Test                     |

| Thermal Shock                 | Tabai                  | Thermal Shock Test           |

| Beam Balance                  | None                   | Weight Measurement           |

| Digital Linear Gauge          |                        | Wafer Thickness Check (IQC)  |

| High Power Microscope w/Video | RCA/Nikon Optiphot     | Wafer Level Inspection       |

| Camera                        | 200                    | Wafer Level Inspection       |

| Ion Coater                    | Eiko Engineering       | SEM Sample Preparation       |

| Solder Pot                    | ESICO                  | Solderability Test           |

| Convection Reflow Oven        | ESSEMTEC               | Package Reflow               |

| Ultrasonic Cleaner            | Branson 1510           | Die cleaning                 |

Table 2-2Summary of QC Test Equipment

| Equipment At Meridian                            | Brand              | Usage                                                                                    |

|--------------------------------------------------|--------------------|------------------------------------------------------------------------------------------|

| Gold Coater                                      | Cressington        | SEM Sample Prep (Backup)                                                                 |

| Low-Speed Diamond Saw                            | Buehler            | Package Cross                                                                            |

| Bench Top Furnace                                | Lindberg           | High Temp Analysis to 1100C                                                              |

| High Temperature Ovens:                          |                    |                                                                                          |

| 175C                                             | Blue M             | Bake Recovering                                                                          |

| 125C                                             | Blue M             | SEM Sample Storage                                                                       |

| Exhaust Hood                                     | Kewaunee           | Chemical Use Safety                                                                      |

| Wet Sink w/Exhaust                               | JST Plastics       | Chemical Use Safety                                                                      |

| Hot Plate PC100                                  | Corning            | Wafer Reliability Analysis                                                               |

| Hot Plate PC100                                  | Corning            | Hot Chemical Etch                                                                        |

| Hot Plate                                        | Lindberg           | Wafer Pressure Pot Test                                                                  |

| Hot Plate                                        | Corning            | Chip Unzip                                                                               |

| Ultrasonic Cleaner (2)                           | Bransonic          | Sample Cleaning                                                                          |

| Etch Automated Dual Acid<br>Decapsulator         | Elite Etch         | Part Decapsulation                                                                       |

| Timers (2)                                       | Gralab             | Timed Operations                                                                         |

| Dial-O-Gram (2)                                  | Ohaus              | Chemical Measurement                                                                     |

| Curve Tracer 576                                 | Tektronix          | Bench Check                                                                              |

| Curve Tracer 577                                 | Tektronix          | Bench Check                                                                              |

| Temperature Forcing Unit                         | Temptronic         | Bench Temperature Testing                                                                |

| Laser Cutter                                     | New Wave EZ LAZE   | Trace Cutting                                                                            |

| FIB With SIMS (SIMS not working)                 | FEI                | Micro Cross Sectioning, Device<br>Modification and Elemental<br>Analysis and Imaging     |

| Reactive ION Etcher (REI), 8-Inch                | Trion              | Device Deprocessing                                                                      |

| Polycon, BF, DF, DIC, Confocal,<br>Fluorescence, | Leica-Reichert     | Product Visual Examination                                                               |

| W/8x8" Stage                                     | Semprex            | Feature Size Measurement                                                                 |

| Visionary 2000                                   | Hypervision        | Emission Microscope,                                                                     |

| Multiprep                                        | Allied High Tech   | Parallel Polishing                                                                       |

| 5x - 100x Optical Microscope                     | Nikon Eclipse L200 | Bright field, Dark field,<br>Numarsky, Confocal inspection,<br>Digital Camera1280 x 1944 |

| High Temperature Oven 20 C - 550 C               | Grieve             | Hammer Testing, Ink Dot Curing                                                           |

Table 2-2Summary of QC Test Equipment (cont'd)

| Equipment At Meridian             | Brand             | Usage                               |

|-----------------------------------|-------------------|-------------------------------------|

| 4156B Precision Semiconductor     | HP                | Parametric Tester                   |

| Parameter Analyzer                |                   |                                     |

| 4274A Multi-Frequency LCR Meter   | HP                | Tester (Inductance, capacitance,    |

|                                   | 111               | resistance instrument)              |

| Microminipulator Test Station (2) | Micromanipulator  | Probe Test                          |

| Philips XL30                      | Philips           | Ultra High Resolution               |

| SFEG SEM                          |                   | SEI, BSE (Solid State)              |

| SMZ-10 Stereo Scope               | Nikon             | External/Internal Visual Inspection |

| XT2-90 XRAY System                | Matrix Focal Spot | Internal Assembly, wire bonding,    |

|                                   |                   | and solder void inspection          |

| Equipment At Milpitas             |                   |                                     |

| Spectrum Analyzer                 | HP-8591A          | Near Field EMI Testing              |

| Pre-Amplifier                     | HP8447D           | Near Field EMI Testing              |

Table 2-2Summary of QC Test Equipment (cont'd)

#### USE OF OUTSIDE FMA LABS

Charles Evans & Assoc. 301 Chesapeake Drive Redwood City, CA 94063

Integrated Service Technology Inc. No. 19, Puding Rd., East District Hsinchu City 300, Taiwan (R.O.C)

#### CUSTOMER NOTIFICATION SYSTEM

Customer Service notifies the customer with a formal change notification letter on major process and design changes. The following is a list of criteria for which all customers are notified:

- Changes to form, fit or function

- Changes to product design and manufacturing locations

- Changes to manufacturing Processes and/or materials

- Changes that may affect product quality, reliability or manufacturability

Customers will be provided with change notification letter that gives the customer a schedule of the conversion, stating that:

The customer will be given 30 days to request qualification samples from Zilog.

New product will be shipped within 60 days from the date of the letter, unless Zilog receives written notice from the customer to continue shipping their current qualified product.

For automotive customers, change notification may be accompanied by a submission of a Product Submission Warrant (PSW) and the necessary attachments (Part Drawing, Failure Mode and Effects Analysis, Engineering Samples) depending if the customer requests that the PPAP process be initiated.

New products for automotive customers will require a PPAP Level 3 Process.

CHAPTER 3, Qualification Requirements

## CHAPTER 3

## Qualification Requirements

DC04-0001 Revision 23 Page 20 of 65

## Zilog An IXYS Company Qualification Requirements

#### **Product/Process Qualification Requirements**

Per Procedures <u>SOP0940</u> and <u>SOP0909</u>, Zilog performs initial qualification on new processes, changes on existing process, new product and changes on existing package following requirements of Table 3-1. Re-qualification is required when material changes occur.

Table 3- 1Product/Process Qualification Requirements

| TEST                           | TEST METHOD                     | CONDITIONS                                           | READPOINTS                       | QUALIFICATIION<br>READPOINT                           | ACC/SS                 |

|--------------------------------|---------------------------------|------------------------------------------------------|----------------------------------|-------------------------------------------------------|------------------------|

| ESD-HBM(3)                     | JESD22-A114<br>current revision | Per Test                                             | N/A                              | N/A                                                   | 2000V Min              |

| ESD-CDM                        | JESD22-C101                     | Per Test                                             | N/A                              | N/A                                                   | Per classification     |

| LATCH-UP(3)                    | JESD78 current revision         | Per Test                                             | N/A                              | N/A                                                   | 0/6<br>@ 200mA<br>min  |

| LIFE TEST                      | MIL-STD-883<br>Method 1005.8    | Condition B, 150°C                                   | N/A                              | 184 hours                                             | 0/77                   |

| LIFE TEST(1)                   | MIL-STD-883<br>Method 1005.8    | Condition B, 125°C                                   | 500 & 1000<br>hours              | 1000 Hours***                                         | 0/77                   |

| TEMPERATURE<br>CYCLE           | JESD22-A104                     | Condition C                                          | N/A                              | 500 Cycles                                            | 0/45                   |

| PRESSURE POT<br>(Autoclave)    | JESD22-A102                     | 121°C/15 PSIG                                        | N/A                              | 96 hours                                              | 0/45                   |

| HAST                           | JESD22-A110                     | 130°C/85%                                            | N/A                              | 96 Hours                                              | 0/45                   |

| FLASH<br>Endurance Test        | JESD22-A117                     | Full specified temp<br>range (min, RT,<br>max temp). | N/A                              | Min. # of specified<br>cycles (typ. 10,000<br>Cycles) | 0/77 per temp<br>range |

| High Temperature<br>Storage(2) | MIL-STD-883<br>Method 1008.2    | 150°C                                                | 500 & 1000<br>Hours              | 1000 Hours (2)                                        | 0/45                   |

| Flash<br>Data Retention (5)    | JESD22-A117                     | 150°C                                                | 500 and 1000<br>hours (168 opt.) | 1000 Hours                                            | 0/77                   |

| MSL<br>Preconditioning<br>(4)  | J-STD-022-A113                  | Per Test                                             | N/A                              | N/A                                                   |                        |

#### PROCESS AND PRODUCT QUALIFICATION REQUIREMENTS

(1) Products that contain FLASH memory must be life tested at 125°C.

(2) This stress is only required for process monitors and qualification of new OTP processes. Devices will be programmed with the checkerboard program, verified and then programmed with inverse checkerboard to program the entire array. Conditional Qualification may be granted for products that require 150°C at 500-hour readout.

(3) The test method originally used to qualify a product may be used if the product is transferred to a different Fab

(4) Preconditioning is required for Temp Cycle, HAST, and PPOT. SOIC/SSOP are rated as MSL 1 PLCC/QFP/LQFP/BGA/QFN(ELP) are rated as MSL 3

(5) This stress is only required for qualification of new flash processes or automotive qualification. QA and product engineering will determine if endurance pre-cycling will be required prior to data retention.

Qualification of new package may require all tests requirements on Table 3-2. A package that has been qualified at one of Zilog's assembly subcontractors is considered to be a new package when run at a different assembly subcontractor. Changes to an existing package may require all the tests listed in Table 3.2.

| <i>Table 3- 2</i>                  |

|------------------------------------|

| Package Qualification Requirements |

#### PACKAGE QUALIFICATION REQUIREMENTS

| TEST                                | TEST METHOD                                         | CONDITIONS            | READPOINTS | QUALIFICATION<br>READPOINT | ACC/SS     |

|-------------------------------------|-----------------------------------------------------|-----------------------|------------|----------------------------|------------|

| LIFE TEST **                        | MIL-STD-883<br>Method 1005.8                        | Condition B,<br>125°C | 168 hours  | 168 hours                  | 0/77       |

| TEMPERATURE<br>CYCLE                | JESD22-A104                                         | Condition C           | N/A        | 500 Cycles                 | 0/45       |

| PRESSURE POT                        | JESD22-A102                                         | 121°C/15 PSIG         | N/A        | 168 Hours                  | 0/45       |

| HAST ***                            | JESD22-A110                                         | 130°C/85%             | 96 Hours   | 96 Hours                   | 0/45       |

| BOND STRENGTH                       | MIL-STD-883<br>Method 2011.7                        | Condition D           | N/A        | N/A                        | 0/10 wires |

| BALL SHEAR                          | JESD22-B116<br>current revision                     | Per Test Method       | N/A        | N/A                        | 0/3 wires  |

| DIE SHEAR                           | MIL-STD-883<br>Method 2019.7                        | Per Test Method       | N/A        | N/A                        | 0/1        |

| PHYSICAL DIM.                       | MIL-STD-883<br>Method 2016                          | Per Test Method       | N/A        | N/A                        | 0/5        |

| LEAD FATIGUE                        | MIL-STD-883<br>Method 2004.5<br>and JESD22-<br>B105 | Per Test Method       | N/A        | N/A                        | 0/1        |

| SOLDERABILITY *                     | MIL-STD-883<br>Method 2003.8                        | Per Test Method       | N/A        | N/A                        | 0/6        |

| X-RAY                               | MIL-STD-883<br>Method 2012.7                        | Per Test Method       | N/A        | N/A                        | 0/32       |

| High Temperature<br>Storage         | MIL-STD-883<br>Method 1008.2                        | 150°C                 | 168 hours  | 168 hours                  | 0/77       |

| MSL<br>Test/Preconditioning<br>**** | J-STD-022-A113                                      | Per Test              | N/A        | N/A                        |            |

| External Visual                     | MIL-STD-883<br>Method 2009.9                        | N/A                   | N/A        | N/A                        | 0/125      |

\* Use 260°C for green package.

\*\* Load samples at High Temperature Storage if there is no available burn-in board.

\*\*\* Could be omitted if there is no available board.

\*\*\*\* Pre-conditioning is required for Temp Cycle, HAST and PPOT. SOIC/SSOP are rated as MSL 1 PLCC/QFP/LQFP/BGA/QFN are rated as MSL 3

#### Zilog Package Qualification Summary

| Lioost .  |                                          |             | 459 Rev.: 01 |

|-----------|------------------------------------------|-------------|--------------|

| ii        | SUMMARY<br>ZiLOG Authorized Distribution | Page 1 of 1 | OP25         |

|           |                                          |             |              |

|           |                                          | DATE:       | 02-08-2006   |

| PRODUCT:  | Z86E0412SEGR538PTR<br>(GREEN Package)    | PROCESS:    | X5220        |

| WRITTEN H | · · · · · · · · · · · · · · · · · · ·    | APPROVED:   | Malie Fonte  |

#### • INTRODUCTION

This report summarizes the qualification results of the Green Package for Delphi Mechatronics. The green package version is compliant to the E.U. RoHS directive.

#### INFORMATION SUMMARY

All qualification tests were performed to MIL-STD-883, JEDEC and/or internal ZiLOG procedures.

#### PRODUCT QUALIFICATION

| Test Description   | Test Method         | Condition   | Test Result         |

|--------------------|---------------------|-------------|---------------------|

| Temperature cycle  | MIL-STD-883/1010    | Condition C | 0/45, 500 cycles    |

| Pressure Pot       | 120 °C, 15 PSI      | Per Test    | 0/45, 168 hours     |

| Package Integrity  | 240 °C, 10 seconds  | Per Test    | 0/15                |

| High Temp Storage  | 150 °C              | Per Test    | 0/77, 168 hours     |

| MSL Classification | Level 1             | Per Test    | 0/22                |

| Burn-in            | 125 °C              | Per Test    | 0/77, 168 hours     |

| Tin Whisker Test   | Room temperature    | Per Test    | Passed, 24 months   |

| Tin Whisker Test   | Dry bake @ 50-55 °C | Per Test    | Passed, 30 months   |

| Tin Whisker Test   | 85 °C /85% RH       | Per Test    | Passed, 18 weeks    |

| Tin Whisker Test   | 30 °C /60% RH       | Per Test    | Passed, 48 weeks    |

| Tin Whisker Test   | Temp Cycle -65 to   | Per Test    | Passed, 1000 cycles |

|                    | 150°C               |             |                     |

| <b>QUALIFICATION</b> | <u>TYPE</u>                                              | DOC. NO.     |

|----------------------|----------------------------------------------------------|--------------|

| Package              | Leadfree (Pure Tin) and Green Compound<br>Qualification  | ZQR-3062067B |

| Device               | Z86E0412SEGR538PTR Green Package<br>Qualification Report | QR-9450      |

ZILOG, Inc. 532 Race Street, San Jose, CA 95126 (T) 408-558-8500

## **CHAPTER 4**

## **Quality Monitor Systems**

Page 25 of 65

Zilog<sup>®</sup> An IXYS Company

## **Quality Monitor Systems**

#### FAILURE RATE PREDICTION CALCULATIONS

Zilog estimates the operating life of our products through statistical methods. It is not possible to guarantee the lifetime of an individual part because the tests to determine this are destructive. Therefore, we can only use statistics to predict the typical behavior of groups of parts. These predictions, and the methods they are based on, are documented in FIT reports. The FIT report is based on process specific data and is derated to reflect individual device characteristics. FIT reports are available for all of Zilog's products.

Other factors that affect device lifetime include actual operating hours, ambient temperature, stability of the power supply, board assembly and other handling practices. All of these factors are outside of the control of Zilog and may dramatically shorten the lifetime of a device.

The failure rate for each product and process is a function of time, temperature and applied power. The primary temperature is, of course, the product junction temperature. This is externally influenced by the ambient temperature and internally influenced by the power dissipated in the die. The power dissipation, in turn, is a function of the duty cycle and applied VCC. In the case of CMOS, product power dissipation is also a function of the operating frequency. Zilog product failure rates were derived from accelerated life test results accumulated on an ongoing basis as part of the Zilog reliability monitor. The accelerated life test reliability data includes both infant mortality (early life results 0-160 hours) and long term life results (168-1000 hours). Various interim time points and sample sizes are used. Life test may be performed at either 125°C for 1000 hours or the Mil Std 883 equivalent or 150°C for 184 hours.

#### **FIT Rate Calculation**

The acceleration obtained when using high temperature life stressing may be calculated for various stress and application temperatures using the widely accepted Arrhenius equation as follows:

$$A = e^{\frac{-E_a(T_1 - T_2)}{kT_1 T_2}}$$

Where:

A = Acceleration factor (dimensionless)

$E_a$  = Activation energy (eV)

$T_1$  = Application junction temperature (K)

$T_2$  = Stress junction temperature (K)

k = Boltzmann Constant 8.617 x 10<sup>-5</sup> (eV/K)

Assume  $E_a = 0.7 \text{ eV}$ , application ambient temperature  $T_a = 55^{\circ}$ C, and stress ambient temperature  $T_s = 125^{\circ}$ C. Consider a typical CMOS product Z84C00 operating with a 100% duty cycle at 8 MHz in a 40 pin PDIP package. With V<sub>CC</sub> = 5.0 V, I<sub>CC</sub> = 40 mA, and package thermal resistance  $\theta_{JA} = 43^{\circ}$ C/W the application junction temperature

$$T_1 = T_a + V_{CC} I_{CC} \theta_{IA} + 273.15$$

and the stress junction temperature

$$T_2 = T_s + V_{CC} I_{CC} \theta_{JA} + 273.15$$

yielding  $T_1$  = 336.75 K and  $T_2$  = 406.75 K. Substituting these values into the above Arrhenius equation gives the acceleration factor

$A = \exp \{-0.7(336.75 - 406.75)/[8.617 \times 10^{-5} (336.75)(406.75)]\} = 63.53$

So 1000 hours of life stress at 125°C is equivalent to 63,530 hours of system application operation at 55°C.

#### FIT and Failure Rate Estimation:

The High Temperature Operating Life (HTOL) stress result is 0 rejects after 561,404 device hours at 125°C. Failure rate estimations are made assuming a Poisson distribution using the  $\chi^2$  density function to assign confidence values as an estimate for the general population as follows:

60% Confidence # Fails = 0 then  $\chi^2$  = 1.85

Given 0 rejects from 561,404 device hours at 125°C, using  $\chi^2$  gives a median failure rate of 1.85/2 rejects per 561,404 device hours or 1.648 reject per 10<sup>6</sup> device hours.

Failure rate =  $1.648/10^6$  device hrs. = 1648 rejects/ $10^9$  device hrs. = 1648 FIT at  $125^\circ$ C Failure rate = 1648/63.53 = 25.94 FIT at  $55^\circ$ C (A = 63.53 as calculated above)

$MTBF = (10^{9}/25.94)/(24^{*}365) = 4401$  years

DC04-0001 Revision 23

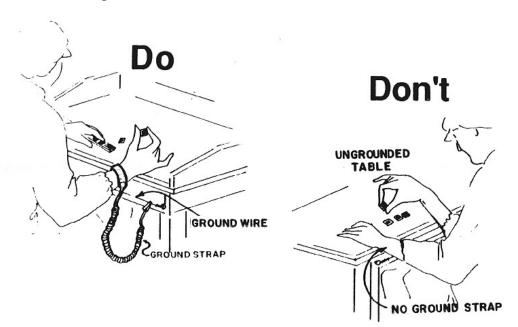

#### ESD TESTING METHODOLOGY

Zilog has an unqualified commitment to quality and reliability and, as part of this commitment; Zilog strives to provide the best possible ESD protection for each of our products.

Since 1983, Zilog has had an ongoing electrostatic discharge development program to monitor and improve its ESD protection circuitry. During an ESD event, the ESD protection circuitry must absorb the power of the ESD pulse while allowing little or no damage to occur to the internal circuitry of the chip. A 3000 volt ESD pulse can induce transient currents approaching one amp, and it is the management of these transient currents that is the key to good ESD protection. At Zilog, ESD protection circuits have been developed to optimize the handling of ESD pulse currents, by paying close attention to current flow patterns, and minimizing current density and crowding problems that cause damage to the circuitry.

All of Zilog's products are tested for their ESD immunity as part of routine internal qualification procedures. The ESD test hardware is in compliance with JEDEC JESD22-A1214B Human Body Model.

#### LATCHUP TESTING METHODOLOGY

Zilog has an unqualified commitment to quality and reliability and, as part of this commitment, also strives to provide each of its products with the best possible latchup protection.

Latchup may occur as a result of either current injection (positive or negative) or supply pin over voltage. The latchup action is that of a parasitic SCR, converting from a high-impedance state, to a low impedance, regenerative, state. The resulting current flow may exceed the design capabilities of the device. Damage may occur to interconnections (bond wires and die metallization) as a result of thermal heating effects and excessive current flow. During conditions which may lead to latchup, the device must be able to shunt the triggering event (the positive or negative injection current) without damage to the device. All of Zilog's products are tested for their latchup immunity per JESD 78 as part of our routine qualification procedure.

#### ZILOG'S RELIABILITY SUMMARY

The tests currently employed under Zilog's reliability monitor include early life (burn-in), steam pressure pot, and temperature cycle.

In addition, a long-term life test is performed on selected lots to gather FIT data. Following are brief descriptions of various reliability tests included in this program.

#### EARLY LIFE

Early Life testing, also called burn-in, is typically performed at 125°C for 168 hours. A dynamic or static bias is employed, depending on the device that is being tested. Early Life test results expose process or assembly defects. These results are a valuable measure of a given fabrication or assembly process.

#### LONG TERM LIFE

Long Term Life testing is generally performed at 150°C for 184 hours or 125°C for 1000 hours. Either dynamic or static bias is used to stress the device appropriately. These test results are used to estimate field operation lifetime for a device. This data can be applied to all products manufactured using the same fabrication process

#### PRESSURE POT

Pressure pot testing is performed at 121°C, 15 PSIG, and 100% relative humidity. This test evaluates the ability of a plastic device to withstand the long-term effects of a humid environment.

#### **TEMPERATURE CYCLE**

Temperature Cycle testing is performed at a  $-65^{\circ}$ C to  $150^{\circ}$ C temperature. This test uses an air-to-air environment. The  $215^{\circ}$ C cold to hot temperature difference determines if proper thermal expansion matching exists between all materials used in device manufacture. The temperature cycle simulates the thermal stresses a device undergoes during power-up and power-down events.

#### HIGHLY ACCELERATED STRESS TEST

The Highly Accelerated Stress Test (HAST) is performed at a 141°C temperature and 85% Relative Humidity (RH) at 2 ATM of pressure with alternate pin bias. This test replaces the traditional 85/85 test and greatly reduces the time taken to evaluate the ability of a plastic encapsulated device to withstand the long-term effects of a biased humid environment.

#### PACKAGE INTEGRITY TEST

Package Integrity testing ensures the integrity of surface mount devices in terms of package cracking, bonding craters, and marked deterioration as a result of heat application during the soldering operation. This includes testing of 5 units on each 3 legs as follows:

| CONTROL | - | 10-SECOND SOLDER DUNK AT 240°C                                              |

|---------|---|-----------------------------------------------------------------------------|

| TEST 1  | - | 10-HOUR *PPT                                                                |

|         |   | 10-SECOND SOLDER DUNK AT 240°C                                              |

| TEST 2  | - | 10-HOUR *PPT<br>3-HOUR OVEN BAKE AT 150°C<br>10-SECOND SOLDER DUNK AT 240°C |

(\*PPT = Pressure Pot Testing at 121°C, 100% RH, 2 ATM)

End-points are room temperature electrical test, visual inspection, mark permanency and crater test. Solder dunk temperature is 260°C for Green Package (G parts, RoHS)

#### Table 4-1

|                              | ZILOG RELIABILITY MONITOR TESTING REQUIREMENTS                                               |                    |                                 |                      |                                                        |  |

|------------------------------|----------------------------------------------------------------------------------------------|--------------------|---------------------------------|----------------------|--------------------------------------------------------|--|

| TEST                         | SAMPLE<br>SELECTION                                                                          | FREQUENCY          | SAMPLE<br>SIZE                  | ALLOWABLE<br>REJECTS | TEST CONDITION                                         |  |

| Temp Cycle or                | Each pkg type per subcon                                                                     | Every six months   | 45                              | 0                    | -65°C +0/-10 to 150°C<br>+15/-0, , 500, 1000<br>cycles |  |

| Thermal<br>Shock**           | Each pkg type per subcon                                                                     | Every six months   | 45                              | 0                    | -55°C +0/-10 to 125°C<br>+10/-0                        |  |

| Pressure Pot                 | Each fab process and<br>each pkg type per<br>subcon                                          | Every six months   | 45                              | 0                    | 168 & 336 hrs, 121°C,<br>100% RH, 2 ATM                |  |

| Burn-in Life                 | Per FAB Process                                                                              | Every three months | 77                              | 0                    | 160 +8/-0 hrs, 125°C or<br>184 hrs, 150°C              |  |

| Test*                        | NMOS/CMOS                                                                                    | Every two months   | 77                              | 0                    | 1000 hrs, cum 125°C or<br>184 hrs, 150°C               |  |

| Package<br>Integrity         | PLCC/QFP, LQFP, ,<br>SOIC, SSOP, QFN per<br>subcon                                           | Every two months   | 15                              | 0                    | Per <u>SOP1656</u>                                     |  |

| ESD                          | Each new die<br>rev/device                                                                   | N/A                | 9 units<br>minimum              | N/A                  | Per JESD22-A114                                        |  |

| Latch up CMOS                | Each new die<br>rev/device                                                                   | N/A                | 6 units<br>minimum              | N/A                  | Per JESD78                                             |  |

| Solderability                | Each pkg type per subcon                                                                     | Monthly            | 6                               | 0                    | Mil Std 883                                            |  |

| Lead Fatigue<br>Test         | Each pkg type per subcon                                                                     | Monthly            | 1 dummy<br>unit                 | 0                    | <u>SOP1662</u>                                         |  |

| DCB<br>Roughness Test        | Per plating subcon                                                                           | Quarterly          | 5 dummy<br>singulated<br>pieces | 0                    | SOP2244                                                |  |

| DCB<br>Solderability<br>Test | For plated - Per<br>plating subcon and<br>assembly<br>For un-plated - Per<br>assembly Subcon | Quarterly          | 6 dummy<br>singulated<br>pieces | 0                    | SOP2244                                                |  |

| DCB<br>Bondability<br>Test   | For plated - Per<br>plating subcon and<br>assembly<br>For un-plated - Per<br>assembly Subcon | Quarterly          | 2 dummy<br>singulated<br>pieces | 0                    | SOP2244                                                |  |

Products that contain FLASH memory require 125C, 1000hrs Burn-in and can be conditionally released after 500hrs. \*\* Thermal shock could be omitted if sampling is done at Temp Cycle.

| DEVICE               | LOT NUMBER        | PLATE 1   | FAB PROCESS         | REJ/SS | CONDITION    |

|----------------------|-------------------|-----------|---------------------|--------|--------------|

|                      |                   |           |                     |        |              |

| S3F80P5XZZ-LM85      | K8D9713F          | S3F80P5   | 0.13um. 2P 5M       | 0/80   | 125ºC/832HRS |

| Z8S18020FEG          | EAGT7163CPA       | Z8S180PB  | X6120               | 0/77   | 150°C/184HRS |

| Z8S18020FEG          | EAGT7163PA        | Z8S180PB  | X6120               | 0/77   | 150°C/184HRS |

| Z8018010FSG          | AGT72172QQQE      | Z80180HA  | X4110               | 0/80   | 150°C/184HRS |

| S3F80RBXZZ-KZ8B-2250 | G4308B015         | S3F80RBAB | 0.11um Eflash 4P 5M | 0/77   | 125°C/500HRS |

| Z8F042ASJ020SG2156   | AACBH147.00E.A    | 8F042ACA  | TSMC                | 0/77   | 125°C/168HRS |

| Z8F022APB020SG       | AACFN043.00QQQA.A | 8F042SAB  | TSMC                | 0/77   | 125°C/168HRS |

| Z84C0006PEG          | AGT75258PE        | Z84C00HB  | X4120               | 0/77   | 150°C/184HRS |

| Z16C0210VSG          | AT80215A.A        | Z16C04BB  | X4120               | 0/77   | 150°C/184HRS |

Table 4-2Burn In Life Test

#### Table 4-3

#### Pressure Pot Test, 121°C, 2 ATM

| PRESSURE POT         |                      |                   |              |         |

|----------------------|----------------------|-------------------|--------------|---------|

| FAB PROCESS          | DEVICE               | LOT #             | DIE STEP     | 168 HRS |

| ASSY LOC: UNISEM-BAT | M                    |                   |              |         |

| X5221                | Z8927320VSG          | AAT74867HS.A      | Z89373CC     | 0/45    |

| X3120                | Z84C2006VEG          | AAT69318QPAA.A    | Z84C20BB     | 0/45    |

| X5220                | Z86E3016SSG          | AT727024HQQQB.A   | Z86E40DG     | 0/45    |

| UMC 0.35um 2P4M      | Z8F1232HJ020SG       | AAR5SSMQQQB.A     | 8F0830AC     | 0/45    |

| X5220                | Z86E4412ASG          | AAT74339HPE.A     | Z86E44AF     | 0/45    |

| TSMC 0.35um          | Z8FS040BSB20EG       | AACGF295.00G.A    | 8F042SAB     | 0/45    |

| TSMC 0.35um          | Z8F022APB020SG       | AACFN043.00QQQA.A | 8F042SAB     | 0/45    |

| X5220                | Z86E4412ASK          | AEAT75256HPQQ2.A  | Z86E44AF     | 0/45    |

| X5220                | Z86E4412ASG          | AEAT75256HPQQ1.A  | Z86E44AF     | 0/45    |

| TSMC                 | Z8F1681QN024XK2247   | AAW3S725.00A.A    | 8F6482AC     | 0/45    |

| X4120                | Z16C0210VSG          | AT80215A.A        | Z16C04BB     | 0/45    |

|                      |                      |                   |              |         |

| ASSY LOC: AMKOR      |                      |                   |              |         |

| X5221                | Z86E8316VEG          | ABT66209HQQQQQPA  | Z86E83BC     | 0/45    |

| X5120                | Z8038018FSG          | ABT51936QQQA      | Z80380CD     | 0/45    |

| ТЅМС                 | Z8F0411PH020SG       | ABCCY982.00IPA    | Z8F082BE     | 0/45    |

| TSMC 0.35 um 2P 4M   | Z16F2811AL020EG      | ABCAF897.00QRC    | 8F1285AB     | 0/45    |

|                      |                      |                   |              |         |

| ASSY LOC: GREATEK    |                      |                   |              |         |

| X4120                | Z84C0006PEG          | AGT75258PE        | Z84C00HB     | 0/45    |

| X4120                | Z84C0010AEG          | AGT75258QPC       | Z84C00HB     | 0/45    |

| X4110                | Z8018010FSG          | AGT72172QQQE      | Z80180HA     | 0/45    |

|                      |                      |                   |              |         |

| ASSY LOC: NANTONG    |                      |                   |              |         |

| 0.13um, 2P 5M        | S3F8S19XZZ-ER89      | 603Y8Y5           | S3F8S19XZZ-W | 0/45    |

| DOTO                 |                      |                   |              |         |

| PSTS<br>0.11um 4P 5M | S3F80RBXZZ-KZ8B-2250 | G4308B015         | S3F80RBAB    | 0/45    |

|                      |                      |                   |              |         |

| 0.13um, 2P 5M        | S3F8S7BXZZ-TW8B      | 603T9Y405         | S3F8S7BXZZ-W |         |

| 0.13um, 2P 5M        | S3F8S7BXZZ-TW8B      | 603T9Y406         | S3F8S7BXZZ-W |         |

| 0.13um, 2P 5M        | S3F8S6BXZZ-QT8B      | 603UPP105         | S3F8S6BXZZ-W |         |

| 0.13um, 2P 5M        | S3F8S6BXZZ-QT8B      | 603UPP104         | S3F8S6BXZZ-V | 0/45    |

#### Table 4-4

#### Temperature/Humidity Test

| TEMP/HUMIDITY TEST |                      |                  |             |               |

|--------------------|----------------------|------------------|-------------|---------------|

| ASSY LOC           | DEVICE               | LOT #            | DIE REV     | <b>RESULT</b> |

| AMKOR              |                      |                  |             |               |

| TSMC 0.35u         | Z16F2811AL20EG       | ABCAF897.00QRC   | 8F1285AB    | 0/22          |

| X5221              | Z86E8316VEG          | ABT66209HQQQQQPA | Z86E83BC    | 0/22          |

| UNISEM-BATAM       |                      |                  |             |               |

| X5221              | Z8927320VSG          | AAT74867HS.A     | Z89373CC    | 0/112         |

| X5220              | Z86E4412ASK          | AEAT75256HPQQ2.A | Z86E44AF    | 0/135         |

| X5220              | Z86E4412ASG          | AEAT75256HPQQ1.A | Z86E44AF    | 0/135         |

| X4120              | Z16C0210VSG          | AT80215A.A       | Z16C04BB    | 0/140         |

| TSMC 0.35u         | Z8FS040BSB20EG       | AACGF295.00G.A   | 8F042SAB    | 0/22          |

| X3120              | Z84C2006VEG          | AAT69318QPAA.A   | Z84C20BB    | 0/22          |

| GREATEK            |                      |                  |             |               |

| X4110              | Z8018010FSG          | AGT72172QQQE     | Z80180HA    | 0/22          |

| X4110              | Z8018010FSG          | AGT72172QQQE     | Z80180HA    | 0/22          |

| NANTONG            |                      |                  |             |               |

| 0.13um, 2P 5M      | S3F8S19XZZ-ER89      | 603Y8Y5          | S3F8S19XZZ- | 0/140         |

| PSTS               |                      |                  |             |               |

| 0.11um 4P 5M       | S3F80RBXZZ-KZ8B-2249 | A66514804V       | S3F80RBAA   | 0/140         |

| 0.11um 4P 5M       | S3F80RBXZZ-KZ8B-2250 | G4308B015        | S3F80RBAB   | 0/45          |

| 0.13um, 2P 5M      | S3F8S7BXZZ-TW8B      | 603T9Y405        | S3F8S7BXZZ- | 0/22          |

| TEMP CYCLE, TEST COND C. |                      |                   |              |             |              |

|--------------------------|----------------------|-------------------|--------------|-------------|--------------|

| ASSY LOC                 | DEVICE               | LOT #             | DIE STEP     | <u>500X</u> | <u>1000X</u> |

| UNISEM-BATAM             |                      |                   |              |             |              |

| X5221                    | Z8927320VSG          | AAT74867HS.A      | Z89373CC     | 0/45        | -            |

| X3120                    | Z84C2006VEG          | AAT69318QPAA.A    | Z84C20BB     | 0/45        | -            |

| X5220                    | Z86E3016SSG          | AT727024HQQQB.A   | Z86E40DG     | 0/45        | -            |

| UMC 0.35um 2P4M          | Z8F1232HJ020SG       | AAR5SSMQQQB.A     | 8F0830AC     | 0/45        | -            |

| TSMC                     | EZ80F91NAA50SG       | AACGV720.00QQQB.A | Z80F91BC     | 0/45        | -            |

| X5220                    | Z86E4412ASG          | AAT74339HPE.A     | Z86E44AF     | 0/45        | -            |

| TSMC 0.35um              | Z8FS040BSB20EG       | AACGF295.00G.A    | 8F042SAB     | 0/45        | -            |

| TSMC 0.35um              | Z8F022APB020SG       | AACFN043.00QQQA.A | 8F042SAB     | 0/45        | -            |

| X5220                    | Z86E4412ASK          | AEAT75256HPQQ2.A  | Z86E44AF     | 0/45        | 0/45         |

| X5220                    | Z86E4412ASG          | AEAT75256HPQQ1.A  | Z86E44AF     | 0/45        | 0/45         |

| TSMC                     | Z8F1681QN024XK2247   | AAW3S725.00A.A    | 8F6482AC     | 0/45        |              |

| X4120                    | Z16C0210VSG          | AT80215A.A        | Z16C04BB     | 0/45        | -            |

|                          |                      |                   |              |             |              |

| AMKOR                    |                      |                   |              |             |              |

| X5221                    | Z86E8316VEG          | ABT66209HQQQQQPA  | Z86E83BC     | 0/45        | -            |

| X5120                    | Z8038018FSG          | ABT51936QQQA      | Z80380CD     | 0/45        | -            |

| TSMC                     | Z8F0411PH020SG       | ABCCY982.00IPA    | Z8F082BE     | 0/45        | -            |

| TSMC 0.35 um 2P 4M       | Z16F2811AL020EG      | ABCAF897.00QRC    | 8F1285AB     | 0/45        | -            |

| GREATEK                  |                      |                   |              |             |              |

| X4120                    | Z84C0010AEG          | AGT75258QPC       | Z84C00HB     | 0/45        | -            |

| X4110                    | Z8018010FSG          | AGT72172QQQE      | Z80180HA     | 0/45        | -            |

| X4120                    | Z84C0006PEG          | AGT75258PE        | Z84C00HB     | 0/45        | -            |

| NANTONG                  |                      |                   |              |             |              |

| 0.13um, 2P 5M Emb Fla    | S3F8S19XZZ-ER89      | 603Y8Y5           | S3F8S19XZZ-V | 0/45        | -            |

| PSTS                     |                      |                   |              |             |              |

|                          | S3F80RBXZZ-KZ8B-2249 | A66514804B        | S3F80RBAA    | 0/45        |              |

| 0.13um, 2P 5M Emb Fla    | S3F8S7BXZZ-TW8B      | 603T9Y405         | S3F8S7BXZZ-  | 0/45        | -            |

| 0.13um, 2P 5M Emb Fla    | S3F8S7BXZZ-TW8B      | 603T9Y406         | S3F8S7BXZZ-  | 0/45        | -            |

Table 4-5

Temperature Cycling Test, Condition C, -65°C To 150°C

| HAST            |                      |                   |                 |               |

|-----------------|----------------------|-------------------|-----------------|---------------|

| ASSY LOC        | DEVICE               | <u>LOT #</u>      | DIE REV         | <u>96 HRS</u> |

|                 |                      |                   |                 |               |

| UNISEM-BATAM    |                      |                   |                 |               |

| UMC 0.35u 2P4M  | Z8F1232HJ020SG       | AAR5SSMQQQB.A     | 8F0830AC        | 0/45          |

| X5220           | Z86E4412ASG          | AAT74339HPE.A     | Z86E44AF        | 0/45          |

| X3120           | Z84C2006VEG          | AAT69318QPAA.A    | Z84C20BB        | 0/45          |

| TSMC 0.35u 2P4M | EZ80F91NAA50SG       | AACGV720.00QQQB.A | Z80F91BC        | 0/45          |

| X4120           | Z16C0210VSG          | AT80215A.A        | Z16C04BB        | 0/45          |

| UMC 0.35u       | Z8F1232HJ020SG       | AAR5SSMQQQB.A     | 8F0830AC        | 0/45          |

| TSMC 0.35u      | Z8FS040BSB20EG       | AACGF295.00G.A    | 8F042SAB        | 0/45          |

| TSMC 0.35u      | Z8F022APB020SG       | AACFN043.00QQQA.A | 8F042SAB        | 0/45          |

|                 |                      |                   |                 |               |

| AMKOR           |                      |                   |                 |               |

| TSMC 0.35u      | Z16F2811AL20EG       | ABCAF897.00QRC    | 8F1285AB        | 0/45          |

| TSMC 0.35u      | Z8F0411PH020SG       | ABCCY982.00IPA    | Z8F082BE        | 0/45          |

|                 |                      |                   |                 |               |

| GREATEK         |                      |                   |                 |               |

| X4120           | Z84C0010AEG          | AGT75258QPC       | Z84C00HB        | 0/45          |

| X4120           | Z84C0006PEG          | AGT75258PE        | Z84C00HB        | 0/45          |

|                 |                      |                   |                 |               |

| NANTONG         |                      |                   |                 |               |

| 0.13um, 2P 5M   | S3F8S19XZZ-ER89      | 603Y8Y5           | S3F8S19XZZ-W0WY | 0/45          |

|                 |                      |                   |                 |               |

| PSTS            |                      |                   |                 |               |

|                 |                      |                   |                 |               |

| 0.13um, 2P 5M   | S3F80RBXZZ-KZ8B-2249 | A66514804B        | S3F80RBAA       | 0/45          |

| 0.13um, 2P 5M   | S3F8S6BXZZ-QT8B      | 603UPP105         | S3F8S6BXZZ-W0WB | 1/45          |

| 0.13um, 2P 5M   | S3F8S7BXZZ-TW8B      | 603T9Y405         | S3F8S7BXZZ-W0WZ | 0/45          |

Table 4-6Highly Accelerated Stress Test (HAST), 140°C, 85% RH, At 2 ATM

| CSAM MONITOR |                |                  |                  |               |

|--------------|----------------|------------------|------------------|---------------|

| ASSY LOC     | DEVICE         | LOT #            | SAMPLE SELECTION | <b>RESULT</b> |

| AMKOR        |                |                  |                  |               |

| TSMC 0.35u   | Z16F2811AL20EG | ABCAF897.00QRC   | Pre-MSL 3        | 0/22          |

| TSMC 0.35u   | Z16F2811AL20EG | ABCAF897.00QRC   | Post MSL 3       | 0/22          |

| X5221        | Z86E8316VEG    | ABT66209HQQQQQPA | Pre-MSL 3        | 0/22          |

| X5221        | Z86E8316VEG    | ABT66209HQQQQQPA | Post MSL 3       | 0/22          |

| UNISEM-BATAM |                |                  |                  |               |

| X5221        | Z8927320VSG    | AAT74867HS.A     | FRESH            | 0/22          |